## LM380 Power Audio Amplifier

National Semiconductor Application Note 69 December 1972

# \_M380 Power Audio Amplifier

### INTRODUCTION

The LM380 is a power audio amplifier intended for consumer applications. It features an internally fixed gain of 50 (34 dB) and an output which automatically centers itself at one-half of the supply voltage. A unique input stage allows inputs to be ground referenced or AC coupled as required. The output stage of the LM380 is protected with both short circuit current limiting and thermal shutdown circuitry. All of these internally provided features result in a minimum external parts count integrated circuit for audio applications.

This paper describes the circuit operation of the LM380, its power handling capability, methods of volume and tone control, distortion, and various application circuits such as a bridge amplifier, a power supply splitter, and a high input impedance audio amplifier.

### CIRCUIT DESCRIPTION

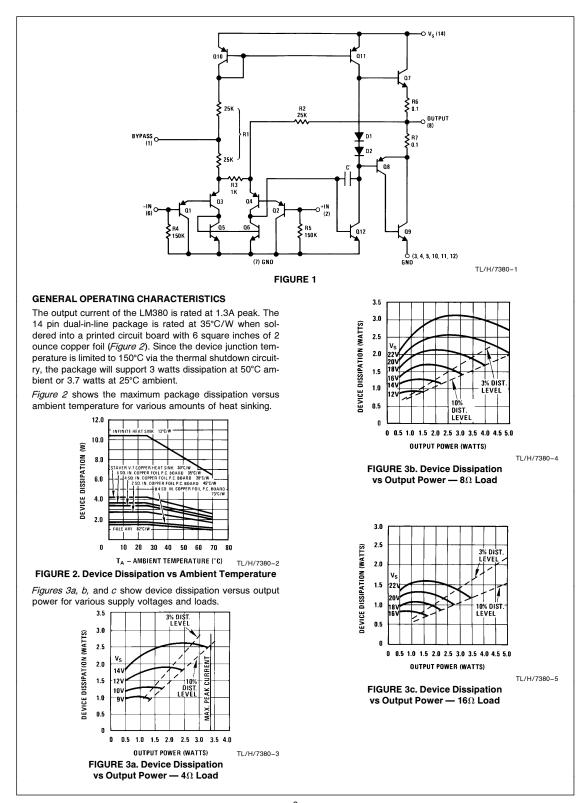

*Figure 1* shows a simplified circuit schematic of the LM380. The input stage is a PNP emitter-follower driving a PNP differential pair with a slave current-source load. The PNP input is chosen to reference the input to ground, thus enabling the input transducer to be directly coupled.

The output is biased to half the supply voltage by resistor ratio  $R_1/R_2$ . Negative DC feedback, through resistor  $R_2$ , balances the differential stage with the output at half supply, since  $R_1 = 2 R_2$  (*Figure 1*).

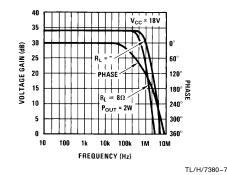

The second stage is a common emitter voltage gain amplifier with a current-source load. Internal compensation is provided by the pole-splitting capacitor C'. Pole-splitting compensation is used to preserve wide power bandwidth (100 kHz at 2W, 8 $\Omega$ ). The output is a quasi-complementary pair emitter-follower.

The amplifier gain is internally fixed to 34 dB or 50. This is accomplished by the internal feedback network R<sub>2</sub>–R<sub>3</sub>. The gain is twice that of the ratio R<sub>2</sub>/R<sub>3</sub> due to the slave current-source which provides the full differential gain of the input stage.

| Parameter                 | Conditions                                                  | Min | Тур  | Max | Units            |

|---------------------------|-------------------------------------------------------------|-----|------|-----|------------------|

| Power Output (rms)        | $8\Omega$ loads, 3% T.H.D. (Notes 3,4)                      | 2.5 |      |     | Wrms             |

| Gain                      |                                                             | 40  | 50   | 60  | V/V              |

| Output Voltage Swing      | $8\Omega$ load                                              |     | 14   |     | V <sub>p-p</sub> |

| Input Resistance          |                                                             |     | 150k |     | Ω                |

| Total Harmonic Distortion | P <sub>o</sub> = 1W, (Notes 4 & 5)                          |     | 0.2  |     | %                |

| Power Supply Rejection    | $C_{bypass} = 5 \ \mu F$ , $\dagger = 120 \ Hz$<br>(Note 2) |     | 38   |     | dB               |

| Supply Voltage Range      |                                                             | 8   |      | 22  | V                |

| Bandwidth                 | $P_0 = 2W, R_L = 8\Omega$                                   |     | 100k |     | Hz               |

| Quiescent Output Voltage  |                                                             | 8   | 9    | 10  | v                |

| Quiescent Supply Current  |                                                             |     | 7    | 25  | mA               |

| Short Circuit Current     |                                                             |     | 1.3  |     | A                |

Note 1:  $V_S$  = 18V;  $T_A$  = 25°C unless otherwise specified.

Note 2: Rejection ratio referred to output.

Note 3: With device Pins 3, 4, 5, 10, 11, 12 soldered into a 1/<sub>16</sub>" epoxy glass board with 2 ounce copper foil with a minimum surface of six square inches. Note 4: If oscillation exists under some load conditions, add a 2.7Ω resistor and 0.1 μF series network from Pin 8 to ground.

Note 5:  $C_{bypass} = 0.47 \ \mu F$  on Pin 1.

Note 6: Pins 3, 4, 5, 10, 11, 12 at 50°C derates 25°C/W above 50°C case.

© 1995 National Semiconductor Corporation TL/H/7380

RRD-B30M115/Printed in U. S. A.

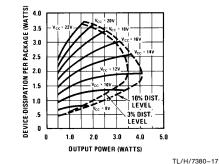

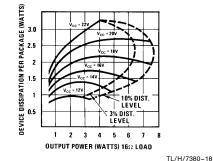

The maximum device dissipation is obtained from *Figure 2* for the heat sink and ambient temperature conditions under which the device will be operating. With this maximum allowed dissipation, *Figures 3a*, *b* and *c* show the maximum power supply allowed (to stay within dissipation limits) and the output power delivered into 4, 8 or 16 $\Omega$  loads. The three percent total-harmonic distortion line is approximately the on-set of clipping.

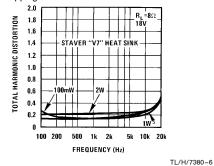

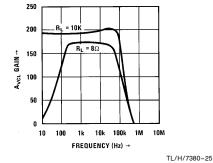

*Figure 4* shows total harmonic distortion versus frequency for various output levels, while *Figure 5* shows the power bandwidth of the LM380.

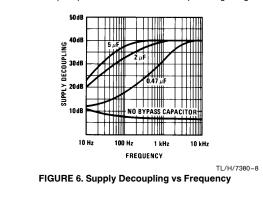

Power supply decoupling is achieved through the AC divider formed by R<sub>1</sub> (Figure 1) and an external bypass capacitor. Resistor R<sub>1</sub> is split into two 25 k $\Omega$  halves providing a high

source impedance for the integrator. *Figure 6* shows supply decoupling versus frequency for various bypass capacitors.

### BIASING

The simplified schematic of Figure 1 shows that the LM380 is internally biased with the 150 k $\Omega$  resistance to ground. This enables input transducers which are referenced to ground to be direct-coupled to either the inverting or non-inverting inputs of the amplifier. The unused input may be either: 1) left floating, 2) returned to ground through a resistor or capacitor or 3) shorted to ground. In most applications where the non-inverting input is used, the inverting input is left floating. When the inverting input is used and the non-inverting input is left floating, the amplifier may be found to be sensitive to board layout since stray coupling to the floating input is positive feedback. This can be avoided by employing one of three alternatives: 1) AC grounding the unused input with a small capacitor. This is preferred when using high source impedance transducer. 2) Returning the unused input to ground through a resistor. This is preferred when using moderate to low DC source impedance transducers and when output offset from half supply voltage is critical. The resistor is made equal to the resistance of the input transducer, thus maintaining balance in the input differential amplifier and minimizing output offset. 3) Shorting the unused input to ground. This is used with low DC source impedance transducers or when output offset voltage is noncritical.

### OSCILLATION

The normal power supply decoupling precautions should be taken when installing the LM380. If V<sub>S</sub> is more than 2" to 3" from the power supply filter capacitor it should be decoupled with a 0.1  $\mu$ F disc ceramic capacitor at the V<sub>S</sub> terminal of the IC.

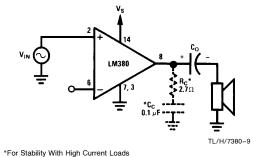

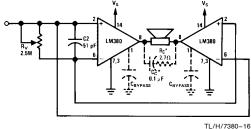

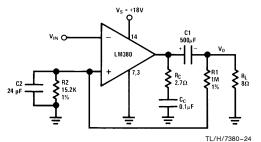

The  $R_C$  and  $C_C$  shown as dotted line components on *Figure* 7 and throughout this paper suppresses a 5 to 10 MHz

FIGURE 7. Minimum Component Configuration

small amplitude oscillation which can occur during the negative swing into a load which draws high current. The oscillation is of course at too high of a frequency to pass through a speaker, but it should be guarded against when operating in an RF sensitive environment.

### APPLICATIONS

With the internal biasing and compensation of the LM380, the simplest and most basic circuit configuration requires only an output coupling capacitor as seen in *Figure 7*.

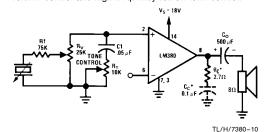

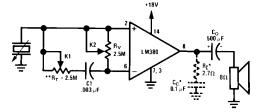

An application of this basic configuration is the phonograph amplifier where the addition of volume and tone controls is required. *Figure 8* shows the LM380 with a voltage divider volume control and high frequency roll-off tone control.

\*For Stability with High Current Loads FIGURE 8. Phono Amp

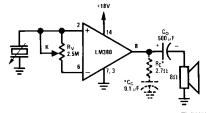

# When maximum input impedance is required or the signal attenuation of the voltage divider volume control is undesirable, a "common mode" volume control may be used as seen in *Figure 9*.

TL/H/7380-11

TI /H/7380-12

### \*For Stability with High Current Loads FIGURE 9. "Common Mode" Volume Control

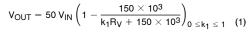

With this volume control the source loading impedance is only the input impedance of the amplifier when in the fullvolume position. This reduces to one-half the amplifier input impedance at the zero volume position. Equation 1 describes the output voltage as a function of the potentiometer setting.

\*For Stability with High Current Loads

\*\*Audio Tape Potentiometer (10% of  $R_T$  at 50% Rotation) **FIGURE 10. "Common Mode" Volume and Tone Control** This "common mode" volume control can be combined with a "common mode" tone control as seen in *Figure 10*. This circuit has a distinct advantage over the circuit of *Figure 7* when transducers of high source impedance are used, in that, the full input impedance of the amplifier is realized. It also has an advantage with transducers of low source impedance since the signal attenuation of the input voltage divider is eliminated. The transfer function of the circuit of *Figure 10* is given by:

$$\frac{V_{OUT}}{V_{IN}} = 50 \left( 1 - \frac{150k}{k_1 R_T k_2 R_V + \frac{k_2 R_V}{j2\pi f c_1}} \right)_{\substack{0 \le k_1 \le 1 \\ 0 \le k_2 \le 1}} (2)$$

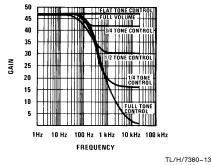

Figure 11 shows the response of the circuit of Figure 10.

### FIGURE 11. Tone Control Response

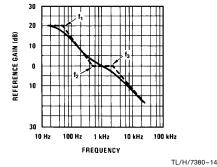

Most phonograph applications require frequency response shaping to provide the RIAA equalization characteristic. When recording, the low frequencies are attenuated to prevent large undulations from destroying the record groove walls. (Bass tones have higher energy content than high frequency tones). Conversely, the high frequencies are emphasized to achieve greater signal-to-noise ratio. Therefore, when played back the phono amplifier should have the inverse frequency response as shown in *Figure 12*.

### FIGURE 12. RIAA Playback Equalization

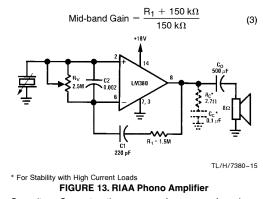

This response is achieved with the circuit of *Figure 13*. The mid-band gain, between frequencies  $f_2$  and  $f_3$ , *Figure 12*, is established by the ratio of  $R_1$  to the input resistance of the amplifier (150 k $\Omega$ ).

Capacitor  $C_1$  sets the corner frequency  $f_2$  where  $R_1 = X_{C1}.$

$$C_1 = \frac{1}{2\pi f_2 R_1} \tag{4}$$

Capacitor  $C_2$  establishes the corner frequency  $f_3$  where  $X_{C2}$ equals the impedance of the inverting input. This is normally 150 kΩ. However, in the circuit of Figure 13 negative feedback reduces the impedance at the inverting input as:

$$Z = \frac{Z_0}{1 + A_0 \beta}$$

(5)

Where:

Zo = impedance at node 6 without external feedback (150 kΩ)

Ao = gain without external feedback (50)

$$\beta$$

= feedback transfer function  $\beta = \frac{A_0 - A}{A_0 A}$

= closed loop gain with external feedback. А Therefore

$$C_{2} = \frac{1}{2\pi f_{3}\left(\frac{Z_{0}}{1 + A_{0}\beta}\right)} = \frac{1}{2\pi f_{3}\left(\frac{150k}{1 + 50\beta}\right)}$$

(6)

### **BRIDGE AMPLIFIER**

Where more power is desired than can be provided with one amplifier, two amps may be used in the bridge configuration shown in Figure 14.

\*For Stability with High Current Loads FIGURE 14. Bridge Configuration

This provides twice the voltage swing across the load for a given supply, thereby, increasing the power capability by a

factor of four over the single amplifier. However, in most cases the package dissipation will be the first parameter limiting power delivered to the load. When this is the case, the power capability of the bridge will be only twice that of

### FIGURE 15A. 8Ω Load

the single amplifier. Figures 15A and B show output power versus device package dissipation for both 8 and 16  $\!\Omega$  loads in the bridge configuration. The 3% and 10% harmonic

distortion contours double back due to the thermal limiting of the LM380. Different amounts of heat sinking will change the point at which the distortion contours bend.

The quiescent output voltage of the LM380 is specified at 9  $\pm$  1 volts with an 18 volt supply. Therefore, under the worst case condition, it is possible to have two volts DC across the load.

### \*For Stability with High Current Loads FIGURE 16. Quiescent Balance Control

With an  $8\Omega$  speaker this 0.25A which may be excessive. Three alternatives are available; 1) care can be taken to match the quiescent voltages, 2) a non-polar capacitor may be placed in series with the load, 3) the offset balance control of Figure 16 may be used.

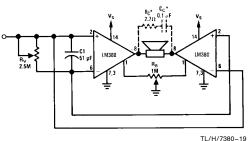

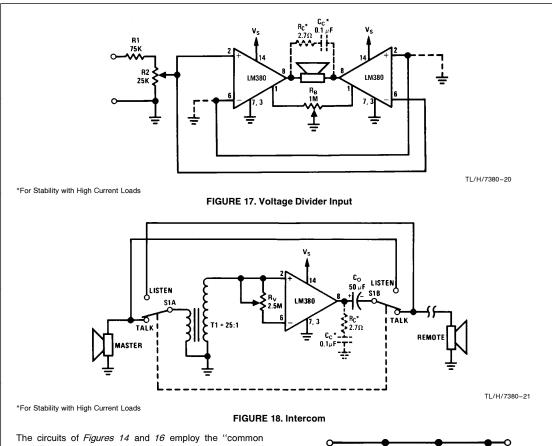

The circuits of *Figures 14* and *16* employ the "common mode" volume control as shown before. However, any of the various input connection schemes discussed previously may be used. *Figure 17* shows the bridge configuration with the voltage divider input. As discussed in the "Biasing" section the undriven input may be AC or DC grounded. If V<sub>S</sub> is an appreciable distance from the power supply (>3") filter capacitor it should be decoupled with a 1  $\mu$ F tantaulum capacitor.

### INTERCOM

The circuit of *Figure 18* provides a minimum component intercom. With switch S<sub>1</sub> in the talk position, the speaker of the master station acts as the microphone with the aid of step-up transformer T<sub>1</sub>.

A turns ratio of 25 and a device gain of 50 allows a maximum loop gain of 1250. R<sub>V</sub> provides a "common mode" volume control. Switching S<sub>1</sub> to the listen position reverses the role of the master and remote speakers.

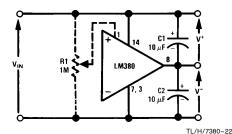

### LOW COST DUAL SUPPLY

The circuit shown in *Figure 19* demonstrates a minimum parts count method of symmetrically splitting a supply voltage. Unlike the normal R, C, and power zener diode tech-

### FIGURE 19. Dual Supply

nique the LM380 circuit does not require a high standby current and power dissipation to maintain regulation.

With a 20 volt input voltage ( $\pm$ 10 volt output) the circuit exhibits a change in output voltage of approximately 2% per 100 mA of unbalanced load change. Any balanced load change will reflect only the regulation of the source voltage V<sub>IN</sub>.

The theoretical plus and minus output tracking ability is 100% since the device will provide an output voltage at one-half of the instantaneous supply voltage in the absence of a capacitor on the bypass terminal. The actual error in

tracking will be directly proportional to the unbalance in the quiescent output voltage. An optional potentiometer may be placed at pin 1 as shown in *Figure 19* to null output offset. The unbalanced current output for the circuit of *Figure 18* is limited by the power dissipation of the package.

In the case of sustained unbalanced excess loads, the device will go into thermal limiting as the temperature sensing circuit begins to function. For instantaneous high current loads or short circuits the device limits the output current to approximately 1.3 amperes until thermal shut-down takes over or until the fault is removed.

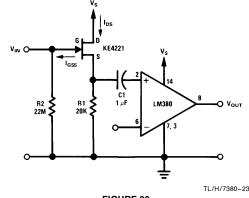

### HIGH INPUT IMPEDANCE CIRCUIT

The junction FET isolation circuit shown in *Figure 20* raises the input impedance to 22 M $\Omega$  for low frequency input signals. The gate to drain capacitance (2 pF maximum for the KE4221 shown) of the FET limits the input impedance as frequency increases.

### FIGURE 20

At 20 kHz the reactance of this capacitor is approximately  $-j4~M\Omega$  giving a net input impedance magnitude of 3.9  $M\Omega$ . The values chosen for R<sub>1</sub>, R<sub>2</sub> and C<sub>1</sub> provide an overall circuit gain of at least 45 for the complete range of parameters specified for the KE4221.

When using another FET device the relevant design equations are as follows:

$$A_{\rm V} = \left(\frac{{\rm R}_1}{{\rm R}_1 + \frac{1}{g_{\rm m}}}\right)$$

(50) (7)

$$g_{m} = g_{m0} \left( 1 - \frac{V_{GS}}{V_{p}} \right)$$

(8)

$$V_{\rm GS} = I_{\rm DS} R_1 \tag{9}$$

$$_{\rm DS} = I_{\rm DSS} \left( 1 - \frac{V_{\rm GS}}{V_{\rm P}} \right)^2 \tag{10}$$

The maximum value of  $R_2$  is determined by the product of the gate reverse leakage  $I_{GSS}$  and  $R_2$ . This voltage should be 10 to 100 times smaller than V<sub>P</sub>. The output impedance of the FET source follower is:

$$R_{o} = \frac{1}{g_{m}}$$

(11)

so that the determining resistance for the interstage RC time constant is the input resistance of the LM380.

### BOOSTED GAIN USING POSITIVE FEEDBACK

For applications requiring gains higher than the internally set gain of 50, it is possible to apply positive feedback around the LM380 for closed loopgains of up to 300. *Figure 21* shows a practical example of an LM380 in a gain of 200 circuit.

### FIGURE 21. Boosted Gain of 200 Using Positive Feedback

The equation describing the closed loop gain is:  $A_{1/C1} = -A_{V(\omega)}$

$$A_{VCL} = \frac{1}{1 - \frac{A_{V(\omega)}}{1 + \frac{R_1}{R_2}}}$$

(12)

where  $A_{V(\omega)}$  is complex at high frequencies but is nominally the 40 to 60 specified on the data sheet for the pass band of the amplifier. If  $1 + R_1/R_2$  approaches the value of  $A_{V(\omega)}$ , the denominator of equation 12 approaches zero, the closed loop gain increases toward infinity, and the circuit oscillates. This is the reason for limiting the closed loop gain values to 300 or less. *Figure 22* shows the loaded and unloaded bode plot for the circuit shown in *Figure 21*.

### FIGURE 22. Boosted Gain Bode Plot

The 24 pF capacitor  $C_2$  shown on *Figure 21* was added to give an overdamped square wave response under full load conditions. It causes a high frequency roll-off of:

$$=\frac{1}{2\pi R_2 C_2} \tag{13}$$

The circuit of *Figure 21* will have a very long (1000 sec) turn on time if  $R_L$  is not present, but only a 0.01 second turn on time with an  $8\Omega$  load.

fo

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.